# Section 65. 12-Bit, High-Speed Pipeline A/D Converter

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 65.1  | Introduction                            |       |

|-------|-----------------------------------------|-------|

| 65.2  | A/D Terminology and Conversion Sequence |       |

| 65.3  | Registers                               |       |

| 65.4  | Operational Overview                    | 65-21 |

| 65.5  | A/D Results Buffer                      |       |

| 65.6  | A/D Trigger Events                      |       |

| 65.7  | Interrupts                              |       |

| 65.8  | Initialization                          |       |

| 65.9  | Sample Lists                            |       |

| 65.10 | Multi-Channel Operation                 |       |

| 65.11 | Threshold Detect Operations             | 65-38 |

| 65.12 | 2 Sample-and-Accumulate Operations      | 65-44 |

| 65.13 | B Effects of a Reset                    |       |

| 65.14 | Operation in Sleep and Idle Modes       | 65-47 |

| 65.15 | 5 Register Map                          |       |

| 65.16 | ን Design Tips                           |       |

| 65.17 | ' Related Application Notes             |       |

| 65.18 | B Revision History                      |       |

# 65.1 INTRODUCTION

The 12-Bit, High-Speed Pipeline A/D Converter module represents a departure from previous PIC24F A/D Converters, incorporating many enhancements for speed and autonomous operation. It is capable of sampling up to once per A/D clock cycle, and supports a wide range of automatic sampling and accumulation options that reduce the need for CPU intervention during even the most complex operations. It also has tighter integration with other on-chip analog modules and a configurable results buffer.

The 12-Bit, High-Speed Pipeline A/D Converter has the following key features:

- Conversion Speeds of up to 10 Msps

- Up to 50 Analog Single-Ended, Input Channels or up to 15 Unique Differential Input Channel Pairs

- Multiple Internal Reference Input Channels

- Multiple Internal and External Voltage Reference Options

- 12-Bit Conversion Resolution

- Automated Threshold Detect (Scan and Compare) Operation to Pre-Evaluate Conversion Results

- Extended, Fully Programmable Channel Scanning Sequences from up to Four Different Sample Lists

- Automated Conversion Result Accumulation

- Selectable Conversion Trigger Source

- · Internal 32-Word, Configurable Conversion Result Buffer

- · Eight Options for Results Alignment

- Configurable Interrupt Generation

- Operation during CPU Sleep, Idle and Doze modes, with Extended Module-Specific Power-Saving Options

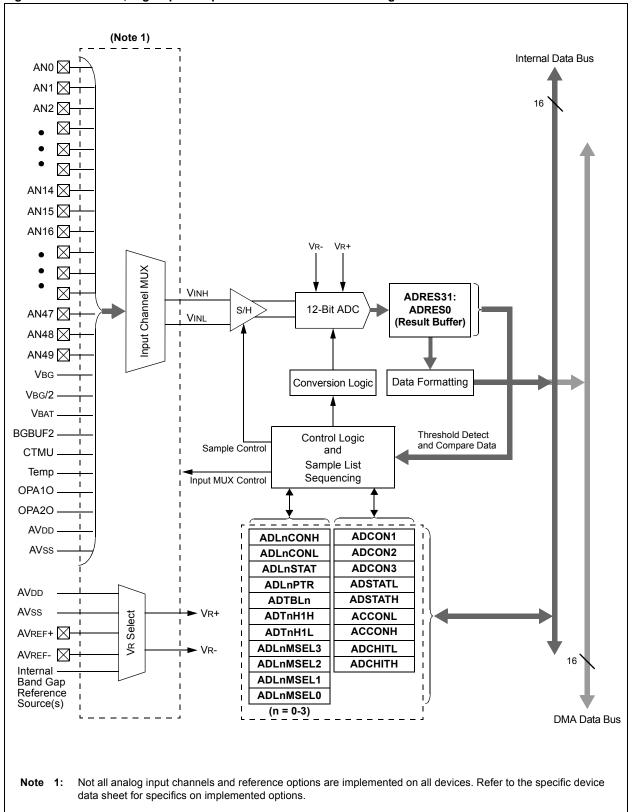

- A simplified block diagram for the module is shown in Figure 65-1.

12-Bit, High-Speed Pipeline A/D Converter

65

# 65.2 A/D TERMINOLOGY AND CONVERSION SEQUENCE

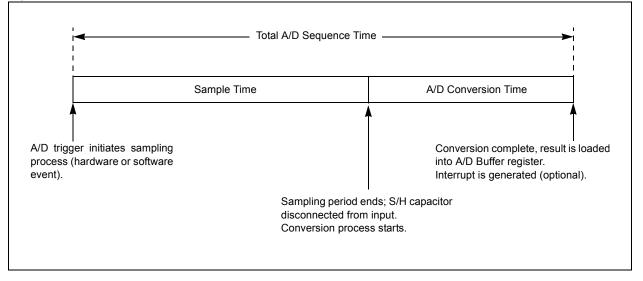

Sample time is the time that the A/D module's Sample-and-Hold (S/H) capacitor is connected to the analog input pin. The sample time is started and ended automatically by the A/D Converter's hardware, in response to a trigger event or under direct program control. There is a minimum sample time to ensure that the S/H capacitor will give sufficient accuracy for the A/D conversion.

The A/D trigger event starts the sampling time. Once this time has elapsed, the hardware automatically begins an A/D conversion. The A/D trigger sources can be taken from a variety of hardware sources or can be controlled directly in software.

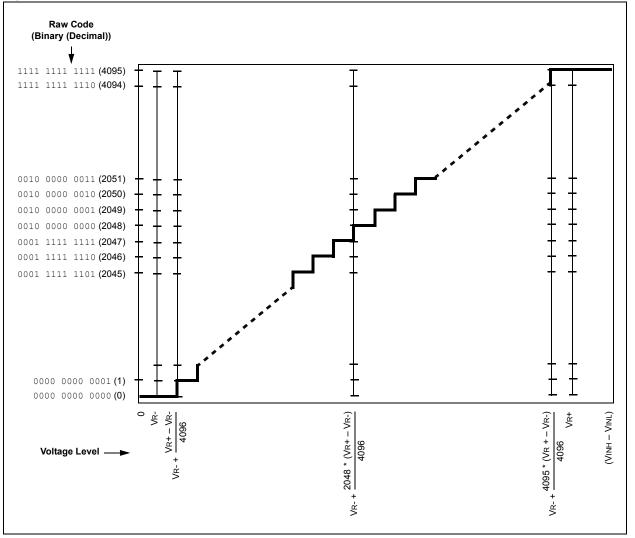

Conversion time is the time required for the A/D Converter to convert the voltage held by the S/H capacitor. When the conversion is complete, the result is loaded into one of the A/D result buffers. A CPU interrupt can also be generated once the conversion result is available. Figure 65-2 shows the basic conversion sequence and the relationship between intervals.

Figure 65-2: A/D Sample/Convert Sequence

# 65.3 REGISTERS

Depending on the specific device, the Pipeline A/D Converter implements up to 151 registers. The majority of these are Sample List Control registers and A/D Results Buffer registers. At a minimum, only six registers need to be programmed to use the module and generate conversion results.

Refer to the specific device data sheet for details on which registers and features are actually implemented.

# 65.3.1 Control Registers

In its full implementation, the Pipeline A/D Converter uses 113 control registers.

Five registers control global operation:

- ADCON1 through ADCON3 (Register 65-1 through Register 65-3) control core A/D operations, including sampling clock rate, selection of voltage references, operation of charge pumps, result buffer configuration, data format and use of Sample Lists.

- ADSTATH and ADSTATL (Register 65-4 and Register 65-5) contain the status flags for top-level module functions, as well as the lower level interrupt flags.

Ninety-six registers control the selection, configuration and execution of the Sample Lists:

- ADLnCONH and ADLnCONL (n = 0 through 3) (prototype registers, Register 65-6 and Register 65-7) configure Sample List operations, including Sample List size, trigger sources, Threshold Detect and Compare mode, and interrupt generation. There is one ADLnCONL and ADLnCONH register for each of the four Sample Lists.

- ADLnSTAT (n = 0 through 3) (prototype register, Register 65-8) contains the status and interrupt flags for the Sample Lists. There is one of each register for each of the four Sample Lists.

- ADLnPTR (n = 0 through 3) (prototype register, Register 65-9) contains the Address Pointer for the Sample List. There is one register for each Sample List.

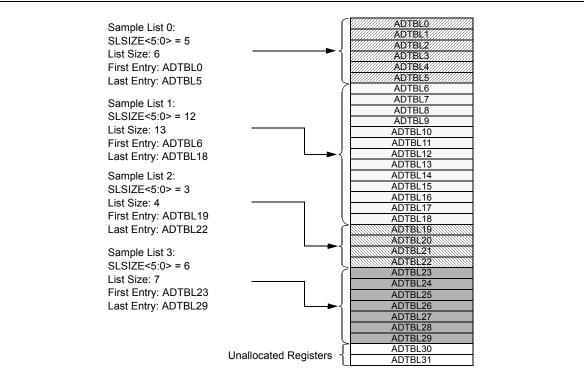

- ADTBLn (n = 0 through up to 63) (prototype register, Register 65-10) configures the sampling and channel selection setup for each item in the Sample List. All implemented registers are available to any of the four Sample Lists.

- ADLnMSELx (n = 0 through 3, x = 0 through 3) (prototypes, Register 65-17 through Register 65-20) selects the analog channels to be used with the Sample Lists for multi-channel sampling. There are four ADLnMSELx registers (ADLnMSEL0 through ADLnMSEL3) for each of the Sample Lists, for a total of 16 registers.

Twelve registers control accumulator and Threshold Detect operations:

- ACCONH and ACCONL (Register 65-11 and Register 65-12) configure the operation of the hardware accumulator.

- AD1CHITH and AD1CHITL (Register 65-13 and Register 65-14) track any positive results per Sample List item during threshold compare operations.

- ADTHnH and ADTHnL (n = 0 through 3) (prototype registers, Register 65-15 and Register 65-16) set the high and low values, respectively, for threshold compare operation on Sample Lists. There are two registers (ADTHnH and ADTHnL) for each Sample List, for a total of 8 registers.

- ADTMRPR is a 16-bit counter that defines the period for the trigger timer. See **Section 65.6.1 "Internal Trigger Timer"** for more details.

# 65.3.2 Data and Buffer Registers

In its full implementation, the Pipeline A/D Converter uses 35 data registers.

ADRES0 through ADRES31 are the memory-mapped result buffers. Depending on the operating and buffer modes selected, the result buffer number may correspond to a particular to an item in a Sample List, or to the item's place in the sampling order. Even though the conversion resolution is 12 bits, result buffers are a full 16 bits wide to accommodate different data formatting options. See **Section 65.5.2 "Buffer Data Formats"** for more information. Depending on the specific device, not all of the 32 result buffers may be implemented.

ACCRESH and ACCRESL store the 32-bit results of hardware Accumulator operations. See **Section 65.12 "Sample-and-Accumulate Operations**" for more details.

| Register   | 65-1: ADCON                                                                                     | 11: A/D Con                                                                                                                  | trol Register                                                                                                                          | 1                                                  |                            |                 |                       |  |  |  |  |

|------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------|-----------------|-----------------------|--|--|--|--|

| R/W-0      | U-0                                                                                             | R/W-0                                                                                                                        | R/W-0                                                                                                                                  | R/W-0                                              | R/W-0                      | R/W-0           | R/W-0                 |  |  |  |  |

| ADON       | —                                                                                               | ADSIDL                                                                                                                       | ADSLP                                                                                                                                  | FORM3                                              | FORM2                      | FORM1           | FORM0                 |  |  |  |  |

| bit 15     |                                                                                                 |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 | bit 8                 |  |  |  |  |

| R/W-0      | R/W-0                                                                                           | U-0                                                                                                                          | U-0                                                                                                                                    | U-0                                                | U-0                        | U-0             | R/W-0                 |  |  |  |  |

| PUMPEI     | (0)                                                                                             |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 | PWRLVL <sup>(3)</sup> |  |  |  |  |

| bit 7      | N ADOAL                                                                                         |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 | bit                   |  |  |  |  |

|            |                                                                                                 |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

| Legend:    |                                                                                                 |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

| R = Reada  |                                                                                                 | W = Writable                                                                                                                 |                                                                                                                                        | •                                                  | nented bit, read           |                 |                       |  |  |  |  |

| -n = Value | at POR                                                                                          | '1' = Bit is se                                                                                                              | t                                                                                                                                      | '0' = Bit is clea                                  | ared                       | x = Bit is unk  | nown                  |  |  |  |  |

| bit 15     | ADON: A/D M                                                                                     | Iodule Enable                                                                                                                | bit                                                                                                                                    |                                                    |                            |                 |                       |  |  |  |  |

|            | 1 = Module is<br>0 = Module is                                                                  |                                                                                                                              | listers are still r                                                                                                                    | eadable and wr                                     | ritable)                   |                 |                       |  |  |  |  |

| bit 14     | Unimplemen                                                                                      |                                                                                                                              |                                                                                                                                        |                                                    | itabic)                    |                 |                       |  |  |  |  |

| bit 13     | ADSIDL: A/D                                                                                     |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

|            | 1 = Halts whe                                                                                   |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

|            |                                                                                                 |                                                                                                                              | CPU Idle mod                                                                                                                           | e                                                  |                            |                 |                       |  |  |  |  |

| bit 12     | ADSLP: A/D                                                                                      | ADSLP: A/D Suspend in Sleep Control bit                                                                                      |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

|            |                                                                                                 | <ul> <li>1 = Continues operation in Sleep mode</li> <li>0 = Ignores triggers and clocks when CPU is in Sleep mode</li> </ul> |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

| bit 11-8   | -                                                                                               | FORM<3:0>: Data Output Format bits                                                                                           |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

|            | 0110 = Fracti<br>0101 = Signe<br>0100 = Intege<br>0011 = Signe<br>0010 = Fracti<br>0001 = Signe | d Fractional (s<br>onal (dddd d<br>d Integer (sss<br>er (0000 dddd<br>d Fractional (s<br>onal (dddd d<br>d Integer (sss      | not use<br>addd dddd dd<br>ddd dddd 00<br>as sddd dddd<br>d dddd ddd<br>addd dddd do<br>ddd dddd 00<br>as sddd dddd 00<br>as sddd dddd | 00)<br>1 dddd)<br>)<br>1dd 0000)<br>00)<br>1 dddd) |                            |                 |                       |  |  |  |  |

| bit 7      |                                                                                                 | -                                                                                                                            | -                                                                                                                                      | Pump Enable I                                      |                            |                 |                       |  |  |  |  |

|            |                                                                                                 |                                                                                                                              | nes is enabled,<br>nes is disabled                                                                                                     | reducing switcl                                    | h impedance <sup>(1)</sup> | )               |                       |  |  |  |  |

| bit 6      |                                                                                                 | -                                                                                                                            | g Calibration bi                                                                                                                       | t <sup>(2)</sup>                                   |                            |                 |                       |  |  |  |  |

|            | 1 = Initiates in<br>0 = No opera                                                                |                                                                                                                              | calibration                                                                                                                            |                                                    |                            |                 |                       |  |  |  |  |

| bit 5-1    | Unimplemen                                                                                      |                                                                                                                              | ·0'                                                                                                                                    |                                                    |                            |                 |                       |  |  |  |  |

| bit 0      | PWRLVL: Po                                                                                      |                                                                                                                              |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

|            | 1 = Full powe                                                                                   | er, maximum c                                                                                                                | onversion rate;                                                                                                                        | A/D clock rates<br>ion; A/D clock r                |                            |                 |                       |  |  |  |  |

| Note 1:    | Use of the channe                                                                               | -                                                                                                                            |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

| 2:         | When set, ADCAI<br>ally clearing the b<br>ADSTATH<1> = 1                                        | it does not ne                                                                                                               |                                                                                                                                        |                                                    |                            |                 |                       |  |  |  |  |

| 3:         | Whenever PWRL                                                                                   |                                                                                                                              | , a delay of 50                                                                                                                        | $\mu S$ should be in                               | nplemented be              | fore the next A | VD conversion         |  |  |  |  |

# Register 65-1: ADCON1: A/D Control Register 1

3: Whenever PWRLVL is set to '1', a delay of 50  $\mu$ S should be implemented before the next A/D conversion.

| Register 6 | 35-2: ADCOM                                 | N2: A/D Cont                              | rol Register      | 2                 |                  |                        |                       |

|------------|---------------------------------------------|-------------------------------------------|-------------------|-------------------|------------------|------------------------|-----------------------|

| R/W-0      | R/W-0                                       | U-0                                       | R/W-0             | U-0               | R/W-0            | R/W-1                  | R/W-1                 |

| PVCFG1     | 1 PVCFG0                                    |                                           | NVCFG0            |                   | BUFORG           | ADPWR1 <sup>(1)</sup>  | ADPWR0 <sup>(1)</sup> |

| bit 15     |                                             |                                           |                   |                   |                  |                        | bit 8                 |

| R/W-0      | R/W-0                                       | U-0                                       | U-0               | U-0               | U-0              | R/W-0                  | R/W-0                 |

| BUFINT1    | <sup>(2)</sup> BUFINTO <sup>(2)</sup>       | _                                         |                   |                   | _                | REFPUMP <sup>(3)</sup> | ADHALT <sup>(1)</sup> |

| bit 7      |                                             |                                           |                   |                   |                  |                        | bit 0                 |

| Legend:    |                                             |                                           |                   |                   |                  |                        |                       |

| R = Reada  | able bit                                    | W = Writable I                            | bit               | U = Unimpler      | mented bit, read | ad as '0'              |                       |

| -n = Value |                                             | '1' = Bit is set                          |                   | '0' = Bit is clea |                  | x = Bit is unkno       | own                   |

|            |                                             |                                           |                   |                   |                  |                        |                       |

| bit 15-14  | <b>PVCFG&lt;1:0&gt;</b><br>11 = Unimple     | : A/D Converte<br>emented                 | r Voltage Refe    | rence Configur    | ration for ADRF  | EF+ bits               |                       |

|            |                                             | band gap source                           | се                |                   |                  |                        |                       |

| bit 13     |                                             | nted: Read as '0                          | 0'                |                   |                  |                        |                       |

| bit 12     | -                                           | D Converter Vol                           |                   | ce Configuratior  | n for ADREF- I   | oit                    |                       |

|            | 1 = External V<br>0 = Avss                  |                                           |                   |                   |                  |                        |                       |

| bit 11     | Unimplemen                                  | nted: Read as 'O                          | 0'                |                   |                  |                        |                       |

| bit 10     | BUFORG: Int                                 | ternal Buffer Or                          | rganization Cor   |                   |                  |                        |                       |

|            | 1 = Internal b                              |                                           | zed as an index   | exed buffer; Cha  |                  | sions are stored       | in Register <i>n</i>  |

| bit 9-8    |                                             | >: A/D Power N                            |                   |                   |                  |                        |                       |

|            | When ADHAL                                  |                                           |                   |                   |                  |                        |                       |

|            | When ADHAL<br>11 = Module r<br>10 = Reserve | <u>LT = 0:</u><br>remains active<br>ed    | in all Power-M    | Aanaged modes     | S                |                        |                       |

|            |                                             | is powered dow is always powe             |                   |                   |                  | erting)                |                       |

| bit 7-6    |                                             | >: FIFO Buffer I                          |                   |                   | 5                |                        |                       |

|            | 10 = Interrupt                              | ot after buffer is f<br>ot when buffer is | s half full       |                   | rs SLEN bit)     |                        |                       |

|            | 00 = No interr                              | •                                         |                   | 11                |                  |                        |                       |

| bit 5-2    | -                                           | nted: Read as 'O                          |                   | (2)               |                  |                        |                       |

| bit 1      |                                             | A/D Reference (                           |                   |                   |                  |                        |                       |

|            | 0 = Referenc                                | ce charge pump<br>ce charge pump          | p is disabled (si |                   |                  |                        |                       |

| bit 0      |                                             | D Suspend bit <sup>(1)</sup>              |                   |                   |                  |                        |                       |

|            | •                                           | triggers and cloo<br>s as normal (cor     |                   |                   |                  | in progress will o     | complete              |

|            | ADHALT and/or A bits may differ. Re         |                                           |                   |                   |                  | cases, the defini      | itions of these       |

| 2:         | BUFINT<1:0> is f                            | forced to '00' wl                         | when the buffer   | r is operating in | Indexed mode     |                        | ).                    |

| 3:         | Use only when the                           | e magnitude of                            | i the A/D refere  | ence is less that | in (0.65 * AVDD  | )).                    |                       |

| Register 65-2: | ADCON2: A/D Control Register 2 |

|----------------|--------------------------------|

|----------------|--------------------------------|

Pipeline A/D Converter 12-Bit, High-Speed

| •                    |                                                                                                                                                                   |                                      | U                    |                                  |                      |                      |                      |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------|----------------------------------|----------------------|----------------------|----------------------|--|--|--|

| R/W-0                | U-0                                                                                                                                                               | U-0                                  | U-0                  | R/W-0, HC                        | R/W-0, HC            | R/W-0, HC            | R/W-0, HC            |  |  |  |

| ADRC <sup>(1)</sup>  | —                                                                                                                                                                 | —                                    | _                    | SLEN3                            | SLEN2                | SLEN1                | SLEN0                |  |  |  |

| bit 15               |                                                                                                                                                                   |                                      |                      |                                  |                      |                      | bit 8                |  |  |  |

|                      |                                                                                                                                                                   |                                      |                      |                                  |                      |                      |                      |  |  |  |

| R/W-0                | R/W-0                                                                                                                                                             | R/W-0                                | R/W-0                | R/W-0                            | R/W-0                | R/W-0                | R/W-0                |  |  |  |

| ADCS7 <sup>(2)</sup> | ADCS6 <sup>(2)</sup>                                                                                                                                              | ADCS5 <sup>(2)</sup>                 | ADCS4 <sup>(2)</sup> | ADCS3 <sup>(2)</sup>             | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |  |  |  |

| bit 7                |                                                                                                                                                                   |                                      |                      |                                  |                      |                      | bit 0                |  |  |  |

|                      |                                                                                                                                                                   |                                      |                      |                                  |                      |                      |                      |  |  |  |

| Legend:              |                                                                                                                                                                   | HC = Hardwar                         |                      |                                  |                      |                      |                      |  |  |  |

| R = Readable         |                                                                                                                                                                   | W = Writable                         | oit                  | •                                | nented bit, read     | d as '0'             |                      |  |  |  |

| -n = Value at        | POR                                                                                                                                                               | '1' = Bit is set                     |                      | '0' = Bit is clea                | ared                 | x = Bit is unkr      | lown                 |  |  |  |

|                      |                                                                                                                                                                   |                                      |                      | × · · · (1)                      |                      |                      |                      |  |  |  |

| bit 15               |                                                                                                                                                                   | Conversion Cloc                      | •                    | ,                                |                      |                      |                      |  |  |  |

|                      |                                                                                                                                                                   | on clock is deri<br>on clock is deri |                      | (TSRC = TFRC)<br>ystem clock (Ts | RC = TSYS)           |                      |                      |  |  |  |

| bit 14-12            |                                                                                                                                                                   |                                      |                      | <b>Jete</b> ele ell (18          |                      |                      |                      |  |  |  |

| bit 11               | Unimplemented: Read as '0'<br>SLEN3: A/D Sample List 3 Enable bit                                                                                                 |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 1 = Sampling for this list is enabled; triggers defined by ADL3CONL<12:8> are processed                                                                           |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 0 = Sampling                                                                                                                                                      | for this list is c                   | lisabled             |                                  |                      |                      |                      |  |  |  |

| bit 10               | SLEN2: A/D Sample List 2 Enable bit                                                                                                                               |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | <ul> <li>1 = Sampling for this list is enabled; triggers defined by ADL2CONL&lt;12:8&gt; are processed</li> <li>0 = Sampling for this list is disabled</li> </ul> |                                      |                      |                                  |                      |                      |                      |  |  |  |

| bit 9                | SLEN1: A/D Sample List 1 Enable bit                                                                                                                               |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 1 = Sampling for this list is enabled; triggers defined by ADL1CONL<12:8> are processed                                                                           |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      |                                                                                                                                                                   | for this list is c                   |                      |                                  |                      |                      |                      |  |  |  |

| bit 8                | SLEN0: A/D Sample List 0 Enable bit                                                                                                                               |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | <ul> <li>1 = Sampling for this list is enabled; triggers defined by ADL0CONL&lt;12:8&gt; are processed</li> <li>0 = Sampling for this list is disabled</li> </ul> |                                      |                      |                                  |                      |                      |                      |  |  |  |

| bit 7-0              |                                                                                                                                                                   | A/D Conversion                       |                      | aler bits <sup>(2)</sup>         |                      |                      |                      |  |  |  |

|                      |                                                                                                                                                                   | (2 * ADCS<7:0                        |                      |                                  |                      |                      |                      |  |  |  |

|                      | 11111111                                                                                                                                                          |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 1111110                                                                                                                                                           |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | ··· = Reserved                                                                                                                                                    |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 00100010<br>00100001                                                                                                                                              |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 00100000 = <b>32 * Tsrc</b>                                                                                                                                       |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 00011111 = ;                                                                                                                                                      | 31 * Tsrc                            |                      |                                  |                      |                      |                      |  |  |  |

|                      |                                                                                                                                                                   |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 00000010 = 4 * TSRC<br>00000001 = 2 * TSRC                                                                                                                        |                                      |                      |                                  |                      |                      |                      |  |  |  |

|                      | 00000000 =                                                                                                                                                        |                                      |                      |                                  |                      |                      |                      |  |  |  |

| Note de Th           | is hit must be a                                                                                                                                                  | at for Sloop on                      | oration              |                                  |                      |                      |                      |  |  |  |

#### Register 65-3: ADCON3: A/D Control Register 3

Note 1: This bit must be set for Sleep operation.

2: Final conversion clock frequency must be between 1 MHz and 10 MHz.

| U-0          | U-0         | U-0               | U-0              | U-0                                     | U-0              | U-0      | U-0    |  |

|--------------|-------------|-------------------|------------------|-----------------------------------------|------------------|----------|--------|--|

|              | —           | —                 |                  | —                                       | —                | —        | —      |  |

| bit 15       |             |                   |                  |                                         |                  |          | bit 8  |  |

|              |             |                   |                  |                                         |                  |          |        |  |

| U-0          | U-0         | U-0               | U-0              | U-0                                     | R-0              | R-0      | R-0    |  |

|              | —           | —                 |                  | —                                       | PUMPST           | ADREADY  | ADBUSY |  |

| bit 7 bit 0  |             |                   |                  |                                         |                  |          |        |  |

|              |             |                   |                  |                                         |                  |          |        |  |

| Legend:      |             |                   |                  |                                         |                  |          |        |  |

| R = Readab   | ole bit     | W = Writable      | bit              | U = Unimplem                            | nented bit, read | l as '0' |        |  |

| -n = Value a | it POR      | '1' = Bit is set  |                  | '0' = Bit is cleared x = Bit is unknown |                  |          | own    |  |

|              |             |                   |                  |                                         |                  |          |        |  |

| bit 15-3     | Unimplemer  | nted: Read as '   | 0'               |                                         |                  |          |        |  |

| bit 2        | PUMPST: A/I | D Boost Pump \$   | Status bit       |                                         |                  |          |        |  |

|              | 1 = The A/D | boost pump is     | active           |                                         |                  |          |        |  |

|              | 0 = The A/D | boost pump is     | Idle             |                                         |                  |          |        |  |

| bit 1        | ADREADY: A  | A/D Analog Rea    | idy bit          |                                         |                  |          |        |  |

|              | 1 = The ana | log portion of th | e A/D is interna | ally calibrated a                       | ind ready        |          |        |  |

|              | 0 = The ana | log portion of th | e A/D is not rea | ady                                     |                  |          |        |  |

| bit 0        | ADBUSY: A/  | D Busy bit        |                  |                                         |                  |          |        |  |

#### ADSTATH: A/D Status Register High Register 65-4:

#### ADBUSY: A/D Busy bit

1 = A/D conversion is in progress

0 = A/D is Idle

# 65

2-Bit, A/D Converter I-Speed

| U-0        | U-0                                                                                                                                                    | U-0                                                                               | U-0              | U-0                           | U-0                           | U-0                           | R/W-0                         |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|--|--|--|--|

| —          | —                                                                                                                                                      | —                                                                                 | —                | —                             | —                             | —                             | SLOV                          |  |  |  |  |

| bit 15     |                                                                                                                                                        |                                                                                   |                  |                               |                               |                               | bit 8                         |  |  |  |  |

|            |                                                                                                                                                        | 5444.0                                                                            |                  | 5444.0                        |                               |                               |                               |  |  |  |  |

| U-0        | U-0                                                                                                                                                    | R/W-0                                                                             | R/W-0            | R/W-0<br>SL3IF <sup>(1)</sup> | R/W-0<br>SL2IF <sup>(1)</sup> | R/W-0<br>SL1IF <sup>(1)</sup> | R/W-0<br>SL0IF <sup>(1)</sup> |  |  |  |  |

| <br>bit 7  | _                                                                                                                                                      | BUFIF                                                                             | ACCIF            | SL3IF <sup>(1)</sup>          | SL2IF***                      | SLIF                          | SLUF(")<br>bit 0              |  |  |  |  |

|            |                                                                                                                                                        |                                                                                   |                  |                               |                               |                               | Dit C                         |  |  |  |  |

| Legend:    |                                                                                                                                                        |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| R = Reada  | ble bit                                                                                                                                                | W = Writable b                                                                    | bit              | U = Unimplem                  | ented bit, read               | 1 as '0'                      |                               |  |  |  |  |

| -n = Value | at POR                                                                                                                                                 | '1' = Bit is set                                                                  |                  | '0' = Bit is clea             | ared                          | x = Bit is unkn               | iown                          |  |  |  |  |

|            |                                                                                                                                                        |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| bit 15-9   | Unimplemen                                                                                                                                             | ted: Read as '0                                                                   | ,                |                               |                               |                               |                               |  |  |  |  |

| bit 8      | SLOV: A/D S                                                                                                                                            | SLOV: A/D Sample List Error Event bit                                             |                  |                               |                               |                               |                               |  |  |  |  |

|            | 1 = A buffer overflow has occurred and data has been lost                                                                                              |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

|            |                                                                                                                                                        | 0 = No buffer overflow has occurred                                               |                  |                               |                               |                               |                               |  |  |  |  |

| bit 7-6    | -                                                                                                                                                      | ted: Read as '0                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| bit 5      | BUFIF: Internal Buffer Interrupt Event bit                                                                                                             |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

|            | <ul> <li>1 = Buffer has been filled to the notification level defined by BUFINT&lt;1:0&gt;</li> <li>0 = Internal buffer has not been filled</li> </ul> |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| bit 4      | <ul> <li>Internal buffer has not been filled</li> <li>ACCIF: Accumulator Counter Interrupt Event bit</li> </ul>                                        |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| DIL 4      | 1 = Accumulator counter has counted down to zero                                                                                                       |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

|            | <ul> <li>a Accumulator counter has not reached zero</li> <li>a Accumulator counter has not reached zero</li> </ul>                                     |                                                                                   |                  |                               |                               |                               |                               |  |  |  |  |

| bit 3      | SL3IF: A/D S                                                                                                                                           | SL3IF: A/D Sample List 3 Interrupt Event bit <sup>(1)</sup>                       |                  |                               |                               |                               |                               |  |  |  |  |

|            |                                                                                                                                                        | 1 = An interrupt event (defined by ADL3CONH<14:13>) has occurred in Sample List 3 |                  |                               |                               |                               |                               |  |  |  |  |

|            |                                                                                                                                                        | rupt event has n                                                                  |                  |                               |                               |                               |                               |  |  |  |  |

| bit 2      |                                                                                                                                                        | ample List 2 Int                                                                  |                  |                               |                               |                               |                               |  |  |  |  |

|            |                                                                                                                                                        | upt event (defin<br>upt event has n                                               |                  | ONH<14:13>) h                 | as occurred in                | Sample List 2                 |                               |  |  |  |  |

| bit 1      |                                                                                                                                                        | ample List 1 Int                                                                  |                  | .;+( <b>1</b> )               |                               |                               |                               |  |  |  |  |

| DILI       |                                                                                                                                                        | upt event (defin                                                                  |                  |                               | as occurred in                | Sample List 1                 |                               |  |  |  |  |

|            |                                                                                                                                                        | upt event has n                                                                   |                  | 0111114.102)11                |                               |                               |                               |  |  |  |  |

| bit 0      |                                                                                                                                                        | ample List 0 Int                                                                  |                  | oit <sup>(1)</sup>            |                               |                               |                               |  |  |  |  |

|            |                                                                                                                                                        | upt event (defin                                                                  | •                |                               | as occurred in                | Sample List 0                 |                               |  |  |  |  |

|            |                                                                                                                                                        | upt event has n                                                                   |                  | ,                             |                               |                               |                               |  |  |  |  |

| Noto 1     | These bits mirror                                                                                                                                      |                                                                                   | aita far tha aar | reconcised ADI                | nOTAT registe                 | ra Changaa in                 |                               |  |  |  |  |

# Register 65-5: ADSTATL: A/D Status Register Low

**Note 1:** These bits mirror the ADLIF flag bits for the corresponding ADLnSTAT registers. Changes in the ADLIF bit are simultaneously reflected in the SLxIF bits.

| Register 65-6: ADLnCONH: A/D Sample List n Control Register High |                                                                                                                                                                                                   |                                                                                                                                                                                                        |                                                                                                              |                                                                          |                   |                 |       |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------|-----------------|-------|--|--|--|

| R/W-0                                                            | R/W-0                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                  | R/W-0                                                                                                        | R/W-0                                                                    | R/W-0             | R/W-0           | R/W-0 |  |  |  |

| ASEN                                                             | SLINT1                                                                                                                                                                                            | SLINT0                                                                                                                                                                                                 | WM1                                                                                                          | WM0                                                                      | CM2               | CM1             | CM0   |  |  |  |

| bit 15                                                           |                                                                                                                                                                                                   |                                                                                                                                                                                                        |                                                                                                              |                                                                          |                   |                 | bit 8 |  |  |  |

| R/W-0                                                            | R/W-0                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                  | R/W-0                                                                                                        | R/W-0                                                                    | R/W-0             | R/W-0           | R/W-0 |  |  |  |

| CTMEN                                                            | PINTRIS                                                                                                                                                                                           | MULCHEN                                                                                                                                                                                                | SAMC4                                                                                                        | SAMC3                                                                    | SAMC2             | SAMC1           | SAMC0 |  |  |  |

| bit 7                                                            |                                                                                                                                                                                                   |                                                                                                                                                                                                        |                                                                                                              |                                                                          |                   |                 | bit 0 |  |  |  |

| Legend:                                                          |                                                                                                                                                                                                   |                                                                                                                                                                                                        |                                                                                                              |                                                                          |                   |                 |       |  |  |  |

| R = Readable                                                     | e bit                                                                                                                                                                                             | W = Writable bi                                                                                                                                                                                        | vit                                                                                                          | U = Unimpler                                                             | mented bit, rea   | ad as '0'       |       |  |  |  |

| -n = Value at                                                    |                                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                       | _                                                                                                            | '0' = Bit is clea                                                        |                   | x = Bit is unkr | nown  |  |  |  |

| bit 15<br>bit 14-13                                              | 1 = Auto-Sca<br>0 = Sequentii<br>SLINT<1:0>:<br><u>When ASEN</u><br>11 = Interrupt<br>10 = Interrupt<br>01 = Interrupt<br>00 = No Interrupt<br><u>When ASEN</u><br>11 = Reserve<br>10 = Interrupt | ot after auto-scan<br>ot after every mate<br>ot after auto-scan<br>rrupt<br>= <u>0:</u><br>ed<br>ot after all records                                                                                  | Convert all as<br>e-and-Conver<br>or Control bits<br>a completion of<br>tch<br>a completion<br>s in a Sample | only if a match o                                                        | ociated input on  | n trigger event |       |  |  |  |

| · = - 4.4                                                        | 01 = Interrupt<br>00 = No interr                                                                                                                                                                  | ot after every sam<br>rrupt                                                                                                                                                                            | nple                                                                                                         |                                                                          |                   |                 |       |  |  |  |

| bit 12-11                                                        | 11 = Reserve<br>10 = No conv<br>01 = Convers                                                                                                                                                      | nternal Buffer Writ<br>ed<br>version results sa<br>sion results saved<br>version results saved                                                                                                         | aved (typically<br>ed when a mat                                                                             | ly for threshold c<br>atch occurs (typi                                  | ically for thresh | hold compare or | • /   |  |  |  |

| bit 10-8                                                         |                                                                                                                                                                                                   | hreshold Compare                                                                                                                                                                                       |                                                                                                              | -                                                                        | 402.              |                 | 4.    |  |  |  |

|                                                                  | 111 = Reserv<br>110 = Reserv<br>101 = Reserv<br>100 = Outside<br>011 = Inside<br>010 = Greate<br>001 = Less T<br>000 = Matchin                                                                    | ved<br>ved<br>le Window Match:<br>Window Match: L<br>er Than Match: A/D I<br>Than Match: A/D I<br>iing is disabled                                                                                     | : A/D Result <<br>Low Thresho<br>A/D Result > T<br>Result < Thre                                             | < Low Threshold<br>old Value < A/D I<br>Threshold Value<br>reshold Value | Result < Three    |                 | •     |  |  |  |

| bit 7                                                            |                                                                                                                                                                                                   | OCTMU Current S                                                                                                                                                                                        |                                                                                                              |                                                                          |                   |                 |       |  |  |  |

|                                                                  |                                                                                                                                                                                                   | <ul> <li>1 = CTMU is enabled during sampling and used as a current source driving the selected analog input</li> <li>0 = CTMU is not used as a current source driving selected analog input</li> </ul> |                                                                                                              |                                                                          |                   |                 |       |  |  |  |

| bit 6                                                            |                                                                                                                                                                                                   | orce Channel TRIS                                                                                                                                                                                      |                                                                                                              | -                                                                        |                   |                 |       |  |  |  |

|                                                                  |                                                                                                                                                                                                   | associated with ch<br>associated with ch                                                                                                                                                               |                                                                                                              |                                                                          |                   | sampling        |       |  |  |  |